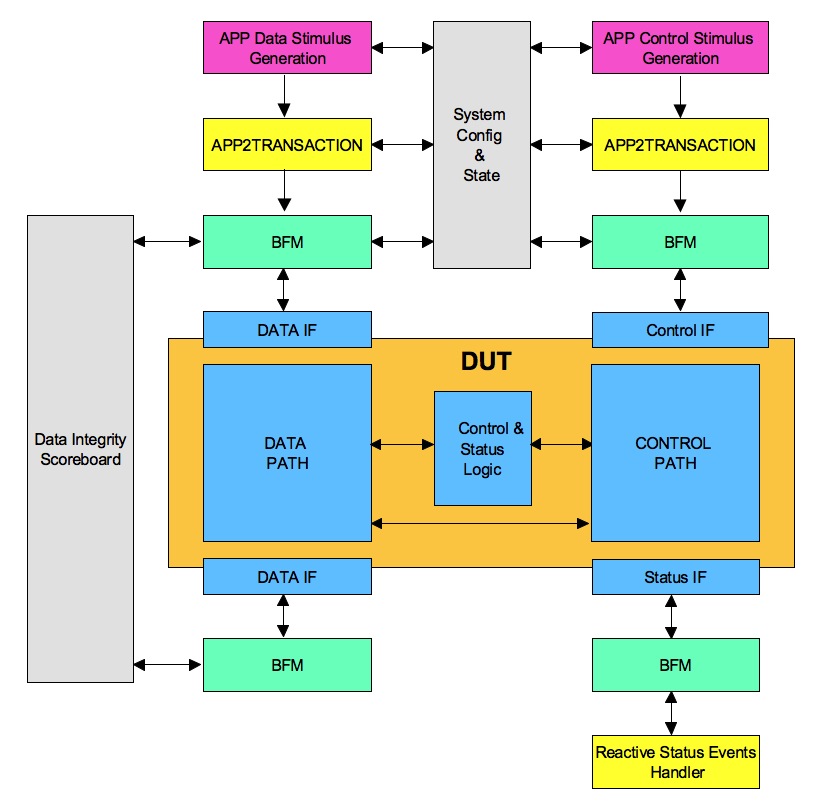

Divide the functionality to various blocks or layers. Map the blocks to classes. Designate the classes as data classes and processing classes. Clearly define the interface between various classes for communicating the information and achieving the synchronization.

Data classes do not have any threads for processing. While processing classes have the single or multiple threads internally to process the data classes.

Data classes help model transaction classes or helper classes. Transaction classes represent a unit of data, which stays together. Example of transaction data class can be protocol data units (PDU) of the bus protocol or image to be processed by image processing engine. Helper classes can come in variety of forms containing various related tasks and functions. They could be forming different types of protocol data units for processing based on discrete information, implementing various encoding & decoding algorithms, managing sequence numbers etc.

For processing classes the number of threads, blocking and unblocking conditions for threads, pseudo code for the functionality of the thread should be specified.

(more…)